#### PARCOURS DE FORMATION SIN – FPGA

Formation des enseignants. Spécialité SIN du baccalauréat STI2D

#### **Christian Dupaty**

Professeur de génie électrique Lycée Fourcade 13120 Gardanne christian.dupaty@ac-aix-marseille.fr http://genelaix.free.fr

## Le microcontrôleur NIOS II

**Christian Dupaty** – académie d'Aix-Marseille <a href="mailto:christian.dupaty@ac-aix-marseille.fr">christian.dupaty@ac-aix-marseille.fr</a> <a href="mailto:http://genelaix.free.fr/">http://genelaix.free.fr/</a>

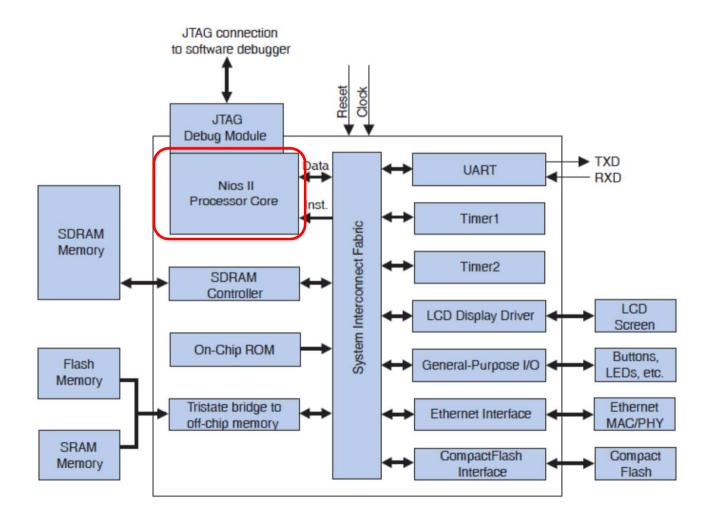

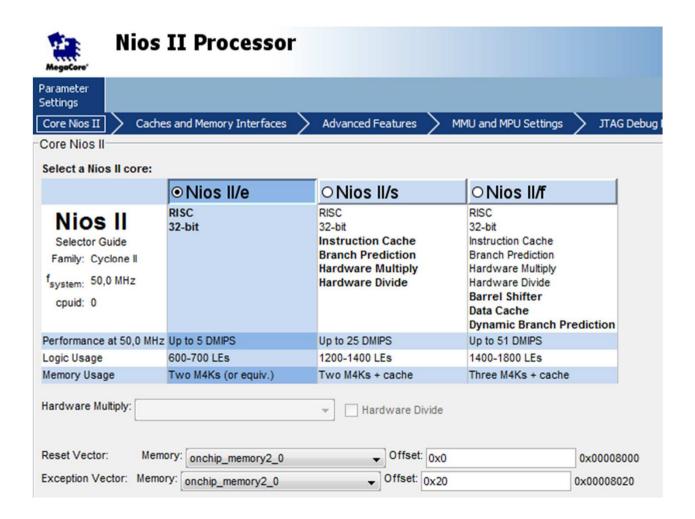

### NIOS II

- Le processeur NIOS II est un composant IP (Intellectuel property) d'ALTERA.

- Processeur 32 bits en technologie RISC

- Trois versions sont proposées suivant la licence disponible.

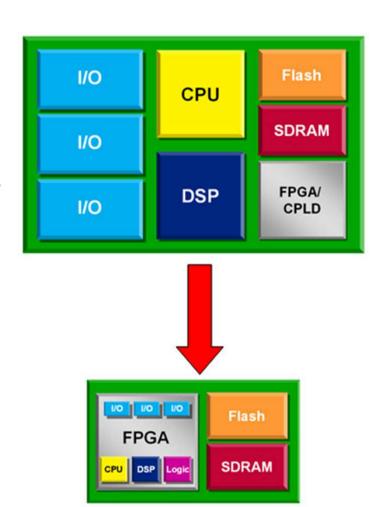

- L'outil de développement crée une description HDL du microcontrôleur et de ses périphériques qui est synthétisable dans un FPGA.

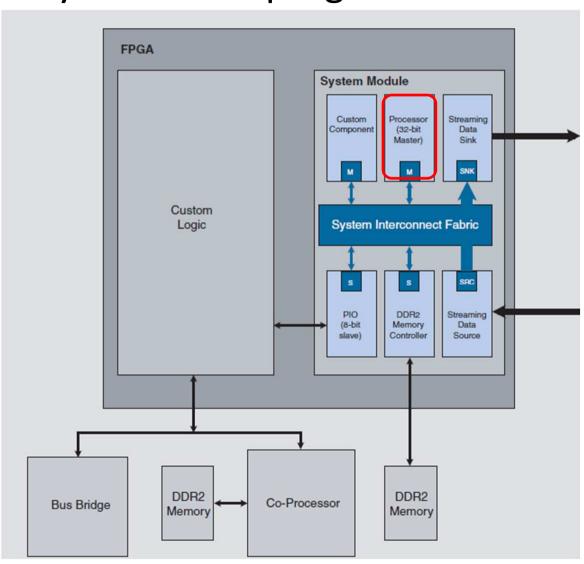

## Exemple de système embarqué

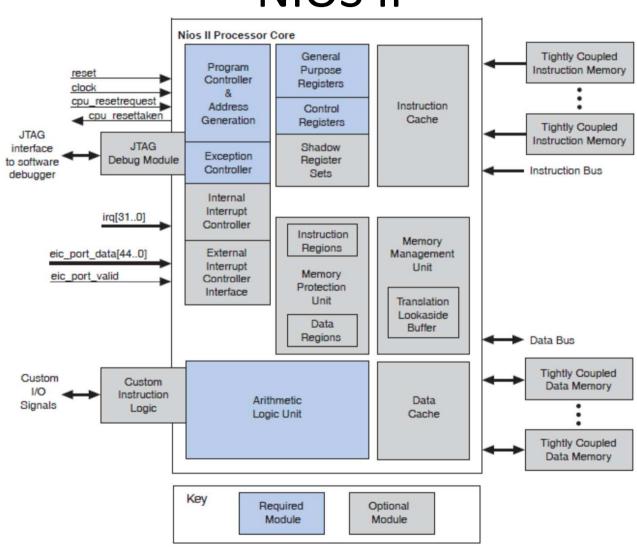

# Structure configurable d'un cœur NIOS II

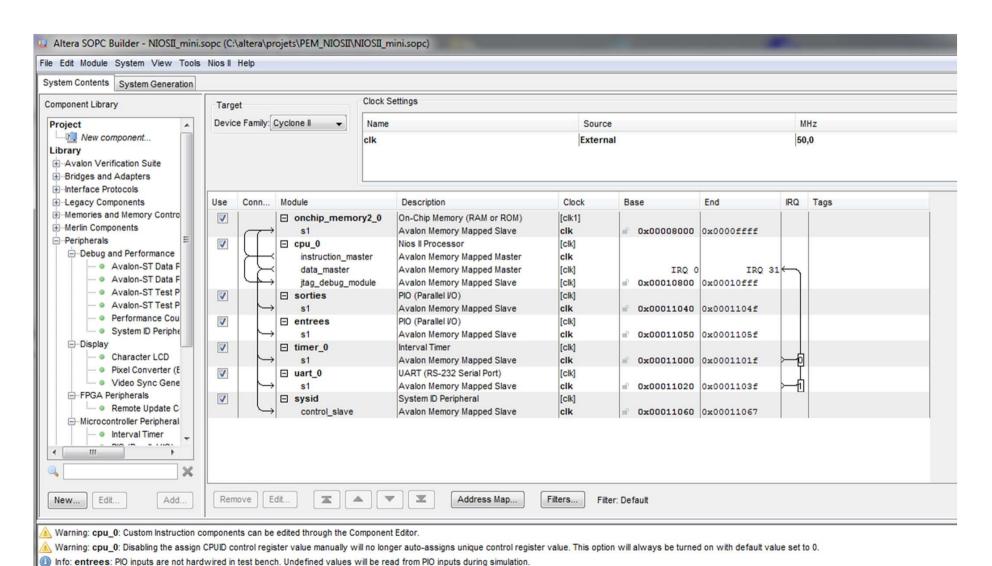

# SOPC system-on-a-programmable-chip

### **SOPC** Builder

## Bibliothèques NIOS II

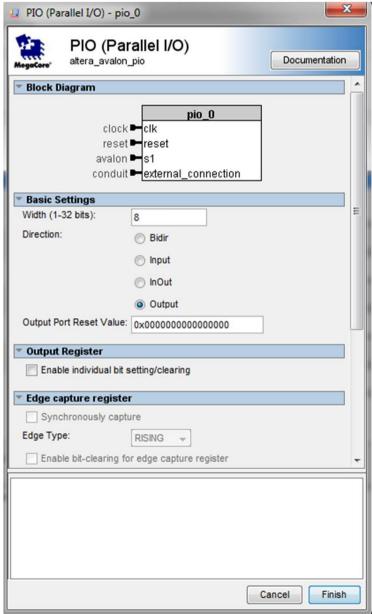

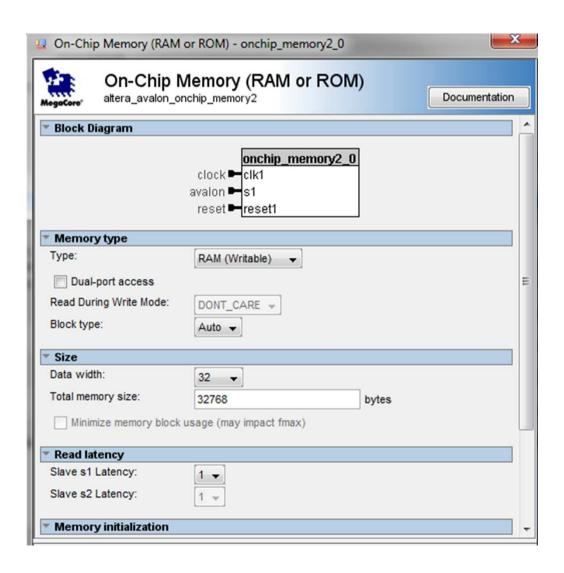

# Bibliothèques périphériques et mémoires

#### **ECLIPSE**

#### Environnement de développement logiciel

```

File Edit Source Refactor Navigate Search Run Project Nios II Window Help

Project Explorer 🛭

demo IT.c 🛭

c system.h

altera avalon timer regs.h

// Demo NIOSII 03-2011

// Christian Dupaty

st tst NIOSII

// Demo IT

Binaries

includes

#include "sys/alt stdio.h"

cobj

#include "system.h"

demo_IT.c

#include "altera avalon pio regs.h"

tst NIOSII.elf - [alteranios.

#include "altera avalon timer regs.h"

create-this-app

#include "sys/alt irq.h"

Makefile

tst NIOSII.map

volatile unsigned int contexte pour IT; // sauvegarde du contexte de l'IT

tst_NIOSII.objdump

st tst NIOSII bsp [NiosII mini]

static void timer flash (void* context)

# Archives

{static unsigned char n=0;

n^=0xFF;

// inverse tous les bits

[ Includes

// efface drapeau d'IT

drivers

//IOWR(TIMER 0 BASE, ALTERA AVALON TIMER STATUS REG, ALTERA AVALON TIMER STATUS TO OFST);

B HAL

IOWR ALTERA AVALON TIMER STATUS (TIMER 0 BASE, ALTERA AVALON TIMER STATUS REG);

a obi

IOWR (SORTIES BASE, 0, n);

c alt sys init.c

h linker.h

h system.h

libhal bsp.a

int main()

create-this-bsp

linker.x

void* Timer IT ptr= (void*) &contexte pour IT;

Makefile

// Une IT est générée lorsque le bit TO du registre status est à 1

mem_init.mk

IOWR (TIMER O BASE, ALTERA AVALON TIMER CONTROL REG, ALTERA AVALON TIMER CONTROL ITO MSK);

memory.gdb

IOWR (TIMER 0 BASE, ALTERA AVALON TIMER PERIODL REG, 0x3E8);

a public.mk

settings.bsp

🚼 Problems 🙋 Tasks 📮 Console 🛭

Properties Debug

summary.html

```

### **INTERRUPTIONS**

- Programmation évènementielles

- Economie de ressources

- Economie d'énergie

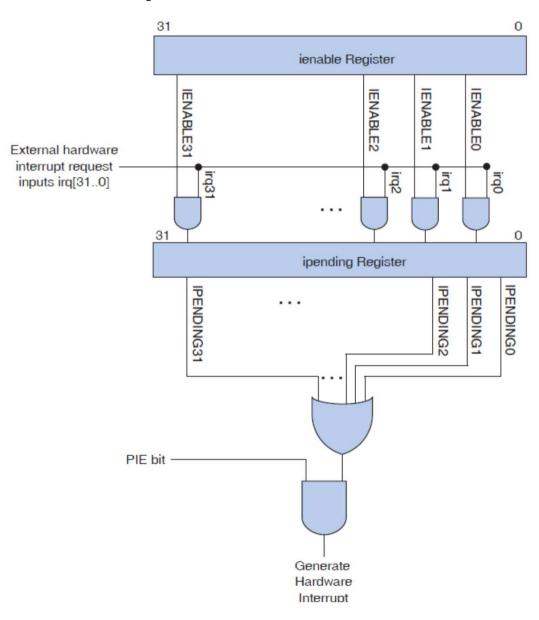

## Principes des IT sur NIOS II

# Exemple: IT sur TIMER

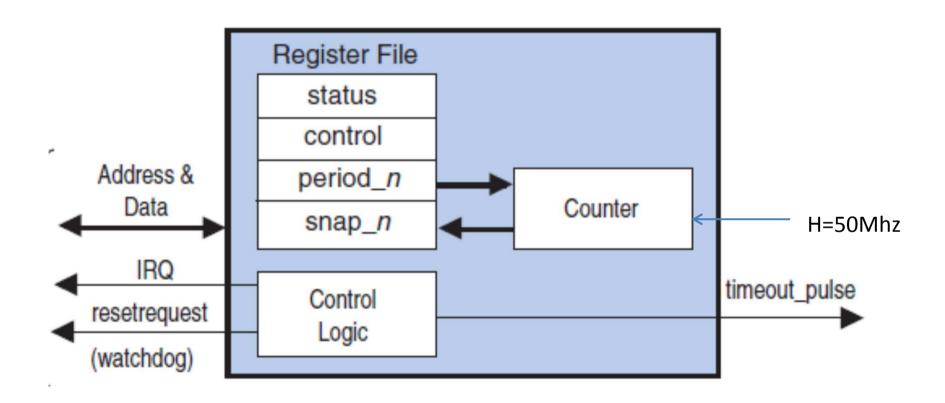

## Registres du TIMER

|        |         |     | Description of Bits               |     |   |      |       |      |     |

|--------|---------|-----|-----------------------------------|-----|---|------|-------|------|-----|

| Offset | Name    | R/W | 15                                |     | 4 | 3    | 2     | 1    | 0   |

| 0      | status  | RW  | (1)                               |     |   |      |       | RUN  | TO  |

| 1      | control | RW  |                                   | (1) |   | STOP | START | CONT | ITO |

| 2      | periodl | RW  | Timeout Period – 1 (bits [15:0])  |     |   |      |       |      |     |

| 3      | periodh | RW  | Timeout Period – 1 (bits [31:16]) |     |   |      |       |      |     |

| 4      | snapl   | RW  | Counter Snapshot (bits [15:0])    |     |   |      |       |      |     |

| 5      | snaph   | RW  | Counter Snapshot (bits [31:16])   |     |   |      |       |      |     |

#### Registre d'état (status)

RUN=1 indique que le TIMER est activé.

TO=1 indique qu'un passage par zéro a eu lieu (il y aura interruption si ITO =1)

#### Registre de contrôle (control)

ITO =1 entraine la génération d'une interruption lors du passage à zéro

CONT =1 entraine un rechargement automatique lors de l'IT

START=1 lance le TIMER.

**Preriodh et periodl**: valeurs initiales du TIMER **Snaph et snapl**: valeurs instantanées du TIMER

## Exemple

Pour générer une IT toutes les 0,5s avec une horloge de 50Mhz

```

control = 0b00000000000111 (7)

period = 0.5*50000000 = 25000000

```

## Gestion de l'interruption

- alt\_ic\_isr\_register(TIMER\_0\_IRQ\_INTERRUPT\_CONTROLLER\_I D,TIMER\_0\_IRQ,timer\_flash,Timer\_IT\_ptr,0);

- TIMER\_O\_IRQ\_INTERRUPT\_CONTROLLER\_ID:

numéro du contrôleur d'IT (ici 0)

TIMER\_O\_IRQ:

numéro d'IT choisie lors de la construction du NIOS II

timer\_flash: sous-programme de gestion de l'interruption

Timer\_IT\_prt: adresse de sauvegarde du contexte (restauré lors du retour d'interruption)