# Technologie des transistors au nitrure de gallium

Matthieu LANDEL<sup>1</sup>

Édité le

01/02/2024

école

normale

supérieure

paris-saclay

<sup>1</sup> Ingénieur à l'IFPEN, docteur de l'Université Paris-Saclay

Cet article fait partie du N°111 de *La Revue 3EI* de janvier 2024.

Cet article vise à donner au lecteur les éléments nécessaires pour appréhender les enjeux de la révolution qui s'opère actuellement en électronique de puissance avec l'arrivée de cette nouvelle technologie de composants, tant en termes de structures de conversion qu'en termes d'enjeux sociaux [1] [2], d'applications et de performances mais aussi de contraintes nouvelles notamment en compatibilité électromagnétique.

Les convertisseurs électroniques de puissance reposent sur des composants à semi-conducteur, et notamment les transistors et les diodes, qui sont réalisés à partir du silicium depuis plus d'un demi-siècle. Remplacer le silicium par des semi-conducteurs à grand gap comme le nitrure de gallium (GaN) est une rupture technologique qui est susceptible de présenter de nombreux avantages [3] [4]. Ainsi, cette nouvelle technologie permet de réduire les pertes par conduction et par commutation, diminuant les besoins de refroidissement. De plus, les transistors GaN commutent très rapidement (à l'échelle de 1-10 ns), ce qui permet d'augmenter la fréquence de travail des convertisseurs et donc de diminuer le volume des éléments passifs. Ainsi, l'adoption du GaN permettrait de réduire le poids des convertisseurs et d'augmenter leur rendement, autrement dit d'accroître leur densité massique de puissance.

## 1 - Propriétés du nitrure de gallium

### 1.1 - Bref historique

Le Nitrate de Gallium (GaN) est un matériau semi-conducteur à grand gap ayant une structure cristalline hexagonale nommée wurzite [8] comme le montre la Figure 1. Cette structure confère au GaN des propriétés piézoélectriques autorisant à l'interface GaN/AlGaN une conductivité supérieure aux autres matériaux semi-conducteurs.

Figure 1 : structure hexagonale du GaN (tiré de [8]).

En 1969, le laboratoire RCA (New York, USA) parvient à déposer du GaN sur un substrat saphir en utilisant la méthode de l'épitaxie en phase vapeur hybride [9]. Il faudra attendre 1993 pour que les premières LED bleues au GaN soient fabriquées. Les transistors GaN à haute mobilité d'électrons (*High Electron Mobility Transistor* ou *HEMT*) sont apparus en 2004 dans le domaine RF (Eudyna Corporation, Japon). Ces transistors avaient un substrat SiC. En 2005, la société Nitronex parvient à faire croître du GaN sur des wafers en silicium. Depuis 2009, on trouve des semiconducteurs de puissance moyenne tension en GaN, grâce aux progrès réalisés sur les matériaux et les procédés de fabrication [4]. A titre d'exemple, la société *EPC* commence à produire des transistors GaN de puissance normalement bloqués cette année-là. Depuis, de grands fondeurs comme Infineon et TI développent de tels transistors.

En comparaison, les *MOSFET* de puissance au silicium ont été introduits en 1976, et ils ont peu à peu remplacé les transistors bipolaires. Il aura fallu environ 30 années pour que les *MOSFET* atteignent leurs limites théoriques en termes de résistance spécifique [3]. La résistance passante spécifique (ou figure de mérite)  $R_{DS,ON} \times S_{active}$  a diminué d'un facteur 50 environ entre l'IRF100 et un *MOSFET* moderne [8]. La fréquence de commutation des *MOSFET* est limitée à quelques centaines de  $kHz$ . Les transistors GaN, eux, permettent d'atteindre des fréquences de l'ordre du  $MHz$  (l'article [3] indique un facteur 30 entre la fréquence de commutation maximale du silicium et celle du GaN).

## 1.2 - Avantages du matériau GaN

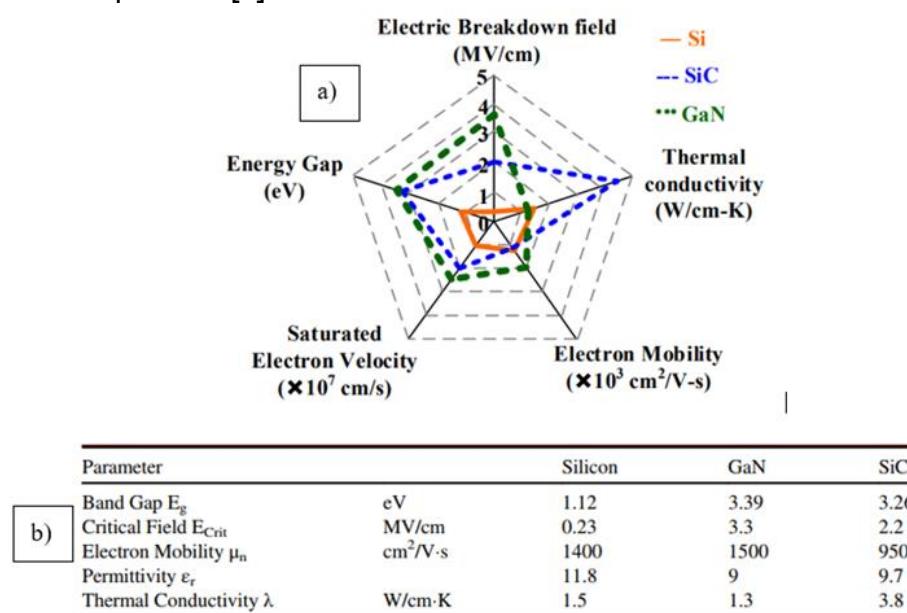

Les composants à semiconducteur jouent un rôle central en électronique de puissance, et le silicium reste aujourd'hui le matériau le plus utilisé. Cependant, les semiconducteurs à grand gap comme le Carbure de Silicium (SiC) et le Nitrure de Gallium (GaN) possèdent des propriétés physiques supérieures [4] [10] [11] [12] [13] [14] [15] [16] [17], comme le montre la Figure 2. Ces semiconducteurs permettent de concevoir des convertisseurs de puissance à plus haut rendement, plus haute température de fonctionnement, plus haute tension et plus haute vitesse de commutation que ceux basés sur les composants au silicium [3] [18] [19] [20]. Aujourd'hui, le matériau GaN est principalement utilisé pour des tensions comprises entre 100  $V$  et 650  $V$ . Au-delà de 1200  $V$ , ce sont plutôt les composants SiC qui sont privilégiés, mais les transistors GaN pourraient bien les remplacer lorsque des composants 1200  $V$  apparaîtront sur le marché, ce qui risque de prendre un certain temps selon [6].

Figure 2 : a) comparaison des propriétés physiques du silicium, du GaN et du SiC (tiré de [10]) ; b) valeurs typiques de ces grandeurs (tiré de [8]).

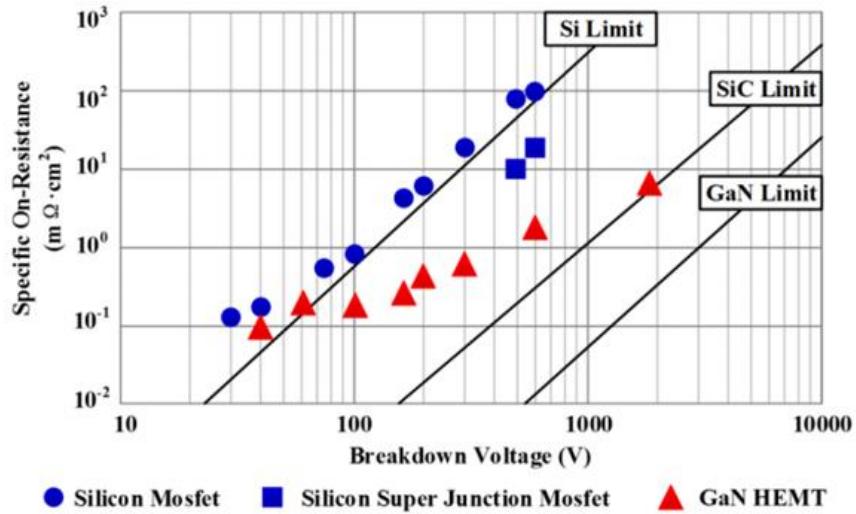

Concentrons-nous sur le GaN. La plupart de ses propriétés physiques sont supérieures à celles du SiC [3], sauf pour la conductivité thermique qui est nettement plus faible. La forte rigidité diélectrique du GaN permet de réduire la distance drain-source du transistor, ce qui diminue la résistance à l'état passant. Cette diminution est encore accrue par la forte mobilité des électrons, notamment dans le gaz d'électrons 2D des transistors au GaN. Ces derniers peuvent ainsi atteindre des résistances passantes spécifiques très inférieures à celles du Si et du SiC (Figure 3). La taille de la puce est ainsi environ dix fois plus faible pour un transistor GaN que pour un transistor Si [3] [21].

Figure 3 : résistance spécifique en fonction de la tension de claquage pour les MOSFETs silicium, les MOSFETs à superjonction et pour les HEMTs au GaN (tiré de [13]).

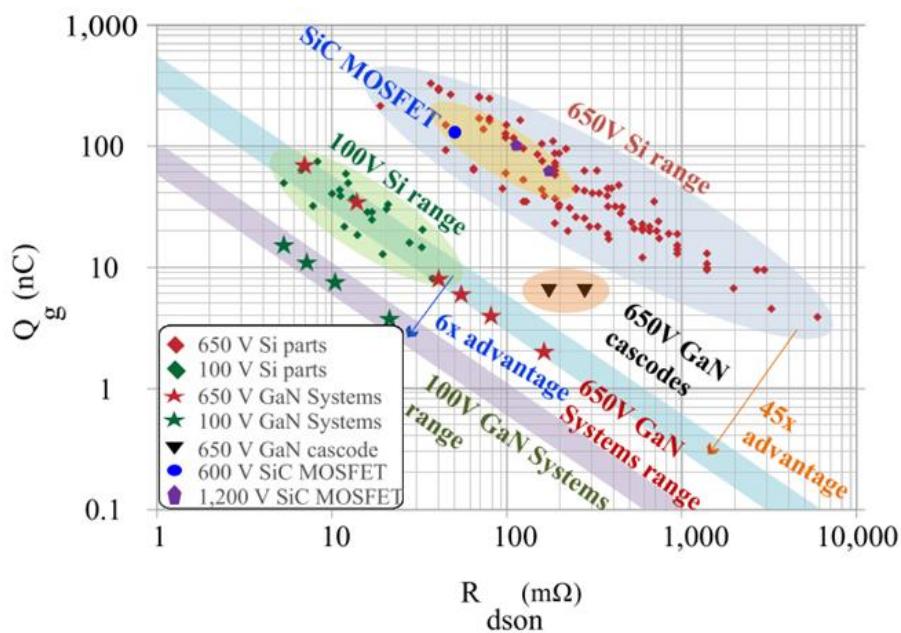

Cet effet de réduction de la taille de la puce (pour un calibre en courant donné) par rapport à un transistor au silicium, a pour conséquence de diminuer les capacités parasites. De plus, la structure latérale des transistors GaN leur procure naturellement une faible capacité de transfert  $C_{GD}$  et une faible capacité  $C_{GS}$  [3] [13]. Ainsi, la capacité d'entrée ( $C_{ISS} = C_{GS} + C_{GD}$ ) est environ 30 fois plus faible pour un transistor GaN que pour un composant au silicium [3] de même caractéristiques et la charge totale de la grille, bien plus faible [13] (Figure 4), explique la diminution des pertes de commande et l'augmentation de la vitesse de commutation. Par ailleurs, la capacité de sortie  $C_{oss}$  est environ dix fois plus faible pour un transistor GaN que pour un MOSFET à superjonction [22].

Figure 4 : charge de grille  $Q_g$  en fonction de la résistance passante pour des transistors Si, SiC et GaN (tiré de [3]).

La vitesse de saturation élevée dans le GaN, combinée avec la faible valeur des capacités parasites, autorise des commutations plus rapides que le silicium. A titre d'exemple, sous 400 V, il est possible de commuter en moins de 10 ns [10]. Le fondeur GaN Systems indique que la vitesse de commutation d'un transistor GaN est quatre fois plus grande à l'amorçage, et deux fois plus grande au blocage par rapport à un transistor SiC [22] de calibre similaire.

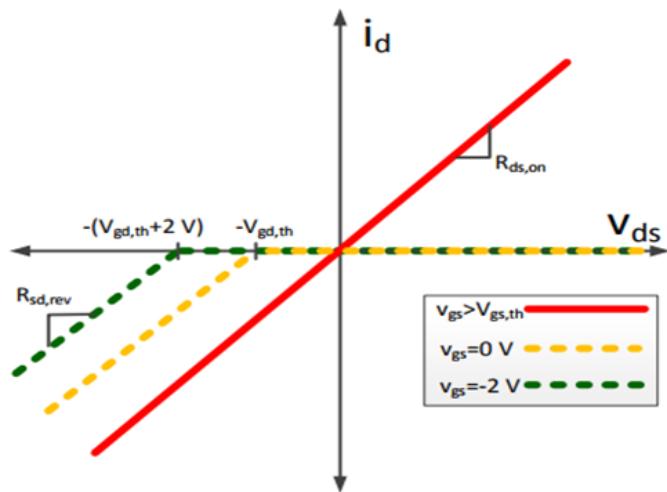

La conduction inverse d'un transistor GaN diffère de celle des *MOSFETs* silicium. Ces derniers possèdent une diode de corps de type PIN, qui est lente et oblige dans la plupart des applications à leur adjoindre une diode antiparallèle de type Schottky ou à les utiliser en mode redresseur synchrone. Du fait de leur structure, les transistors GaN n'ont pas de diode de corps, et donc pas de pertes par recouvrement inverse. En revanche, ces transistors présentent une chute de tension source-drain en conduction inverse lorsque la tension grille-source  $V_{GS}$  est inférieure à la tension de seuil  $V_{TH}$ , comme le décrivent Jones et al. dans [10]. La chute de tension est égale à :  $V_{SD} = V_{TH} - V_{GS-OFF}$ . Utiliser une tension  $V_{GS}$  négative permet de bloquer efficacement le composant mais cela augmente donc les pertes en conduction inverse.

Figure 5 : caractéristique  $I_D = f(V_{DS})$  pour un transistor GaN conduisant en inverse (tiré de [10]).

Enfin, du fait de leurs structures, la tension de seuil des différentes familles de transistors GaN est plus basse qu'un transistor *MOSFET* Si (1,5 V environ pour un transistor GaN 650 V, contre 4 V pour un *MOSFET* Si 650 V), et la tension de grille optimale est de 5 V à 6 V seulement [22], ce qui diminue aussi les pertes de commande car les *IGBTs*, les *MOSFETs* silicium et SiC nécessitent des tensions de l'ordre de 15 à 20 V (Tableau 1).

Tableau 1 : comparaison des tensions de commande des transistors GaN de GaN Systems avec les *MOSFETs* Si, les *IGBT* et les *MOSFETs* SiC [18].

| Gate Bias Level          | GaN Systems<br>GaN E-HEMT | Si MOSFET | IGBT         | SiC MOSFET |

|--------------------------|---------------------------|-----------|--------------|------------|

| Maximum rating           | -20/+10V                  | -/+20V    | -/+20V       | -8/+20V    |

| Typical gate bias values | 0 or -3/+5-6V             | 0/+10-12V | 0 or -9/+15V | -4/+15-20V |

Le GaN est donc un très bon candidat pour des applications à fort rendement et/ou de découpage à haute fréquence [23]. Dès 2013, l'article [24] indiquait que ces transistors commençaient déjà à se répandre sur le marché grâce à leurs propriétés supérieures à celles du silicium.

### 1.3 - Importance du substrat

Une étape cruciale dans la fabrication d'un transistor GaN est le dépôt du GaN sur un substrat. Ce dernier peut être du GaN (homo-épitaxie) ou bien un matériau étranger (hétéro-épitaxie).

L'homo-épitaxie sur substrat GaN est la solution idéale structurellement parlant [25] et assure une faible densité de défauts cristallins, mais sa fabrication est difficile. La méthode Czochralski (utilisée avec succès pour faire croître du silicium) n'est pas adaptée car elle demanderait de très hautes température et pression [4]. L'épitaxie hybride en phase vapeur (HVPE) sur un matériau étranger comme le saphir reste la méthode la plus utilisée, par exemple dans [26]. Elle est décrite en détails dans [27] où les auteurs fabriquent un wafer de GaN de trois pouces. Le saphir est ensuite supprimé. D'autres techniques permettent de se passer de ce matériau étranger et font l'objet de recherches [10] : la méthode *HNPSG* (*High Nitrogen Pressure Solution Growth*), la méthode Na-Flux (solution à basse pression avec du sodium) et la méthode ammonothermale, qui semble prometteuse en termes de coût dans un futur proche. Dans l'article [28] de 2021, les auteurs présentent une technique innovante nommée FFC, mélange de la technique « Na Flux » et HVPE ; ils fabriquent ainsi un wafer GaN de deux pouces. La fabrication de ces derniers est encore un sujet actif de recherche.

L'hétéro-épitaxie est moins coûteuse et c'est la solution retenue industriellement aujourd'hui. Le GaN est généralement déposé par hétéro-épitaxie sur un matériau étranger comme le SiC, le saphir ou le silicium, mais les distances atomiques et les propriétés thermiques du GaN sont différentes de ces derniers, ce qui engendre des contraintes et des dislocations [4] [3]. Il est donc nécessaire de placer une couche tampon sur le substrat, qui absorbe les contraintes mécaniques. Des couches alternées de GaN, d'AlGaN et d'AlN peuvent être utilisées [10], formant une épaisseur totale de quelques micromètres. La Figure 6 présente les caractéristiques physiques de trois matériaux pouvant être utilisés comme substrat.

|                                                                                            | SiC                     | Sapphire                | Si                      |

|--------------------------------------------------------------------------------------------|-------------------------|-------------------------|-------------------------|

| Lattice constant mismatch                                                                  | 3.1%                    | 15%                     | 17%                     |

| Linear thermal expansion coefficient ( $\times 10^{-6} \text{ K}^{-1}$ ) (GaN value = 5.6) | 4.16 (c-axis)           | 7.5                     | 2.6                     |

| Thermal conductivity ( $\text{W cm}^{-1} \text{ K}^{-1}$ )                                 | 3.8–4.9                 | 0.25                    | 1.56                    |

| Typical epitaxial GaN dislocation density                                                  | $>10^8 \text{ cm}^{-2}$ | $>10^8 \text{ cm}^{-2}$ | $>10^9 \text{ cm}^{-2}$ |

| Cost                                                                                       | Expensive               | Less expensive          | Cheap                   |

Figure 6 : comparaison des substrats possibles pour un transistor GaN (tiré de [4]).

Le SiC est le meilleur choix, mais reste très cher. On le réserve aux très hautes densités de puissance. Le saphir est moins cher mais sa conductivité thermique est très inférieure au SiC. De plus, les wafers de saphir sont limités à une taille de deux pouces. Pour des applications commerciales sensibles au coût, le substrat Si est un bon compromis [3], et les wafers sont disponibles en grand diamètre. Pour rester compétitifs, les transistors GaN doivent être fabriqués sur des wafer de diamètre 150 mm minimum (comme c'est le cas dans [29]), sachant que les *IGBTs* Si sont fabriqués sur des wafers de 200 mm voire 300 mm en pleine production. L'article [30] présente ainsi la fabrication de transistors GaN sur un wafer silicium de 300 mm. On réalise une hétéro-épitaxie par *MOCVD* (*Metal Organic Chemical Vapor Deposition*). La suite des étapes de fabrication du transistor dépend de la structure choisie (partie 2 - ).

Les transistors GaN sont pour l'heure encore coûteux, mais leur diffusion massive devrait permettre de réduire leur prix [3], peut-être au niveau de celui du silicium [19].

## 2 - Structures de transistors GaN de puissance

Les transistors GaN normalement passants peuvent être utilisés pour des applications basse tension à haute fréquence de commutation, mais le domaine de l'électronique de puissance exige un comportement normalement bloqué pour des raisons de sécurité [3] [10] [20] [23]. Cela permet aussi de simplifier la commande du transistor. Nous allons nous focaliser sur ce type de composants.

Les structures verticales sont également prometteuses, nous les aborderons brièvement dans la partie 2.2 - .

## 2.1 - HEMT (HFET)

Ces transistors seront désignés par le terme *HEMT* (*high electron mobility transistor*), même si on trouve le terme *HFET* (*Heterojunction Field Effect Transistor*) dans la littérature, qui est équivalent.

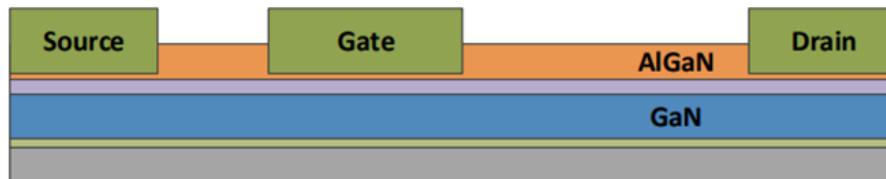

### 2.1.1 - HEMT à grille gravée (recessed gate)

La structure *HEMT* est la plus étudiée et la plus répandue chez les industriels [10]. Elle est basée sur un phénomène spontané de polarisation piézoélectrique apparaissant à l'interface d'une hétérostructure AlGaN/GaN [8] [10]. La couche d'AlGaN a une épaisseur généralement comprise entre  $20\text{ nm}$  et  $30\text{ nm}$ . Un gaz 2D d'électrons très dense et à haute mobilité ( $1500 - 2000\text{ cm}^2.\text{V}^{-1}.\text{s}^{-1}$  [8]) est alors créé. Les *HEMTs* sont ainsi de très bons candidats pour des applications de forte puissance et/ou de découpage haute fréquence. Cependant, le gaz 2D rend ces transistors normalement passants. Le canal existe en permanence, même en l'absence d'une polarisation de grille positive.

Il existe plusieurs façons d'appauprir le gaz 2D et ainsi fabriquer un transistor normalement bloqué, chacune ayant ses limitations et ses compromis [4] [23]. La méthode la plus répandue est de graver partiellement la couche d'AlGaN pour y loger la grille (*recessed gate*). On amincit en général cette couche uniquement sous la grille, en gravant avec du plasma (méthode *ICP-RIE* pour *Inductive Coupled Plasma Reactive Ion Etching* [31]). La concentration en aluminium de la couche d'AlGaN peut aussi être modifiée. La gravure diminue l'effet piézoélectrique et coupe le gaz 2D. La structure *HEMT* est assez difficile à fabriquer car elle exige un contrôle précis de la profondeur de gravure, ce paramètre influant directement sur la tension de seuil [23]. Si la gravure est mal contrôlée, cela peut générer un courant de fuite de grille et impacter l'uniformité de la tension de seuil. La Figure 7 montre la structure d'un *HEMT* à grille gravée.

Figure 7 : structure *HEMT* à grille gravée, où la couche d'AlGaN est gravée partiellement pour recevoir la grille (tiré de [10]).

Les *HEMTs* de ce type présentent de très faibles valeurs de résistance à l'état passant.

### 2.1.2 - MOS-HEMT (ou MIS-HEMT)

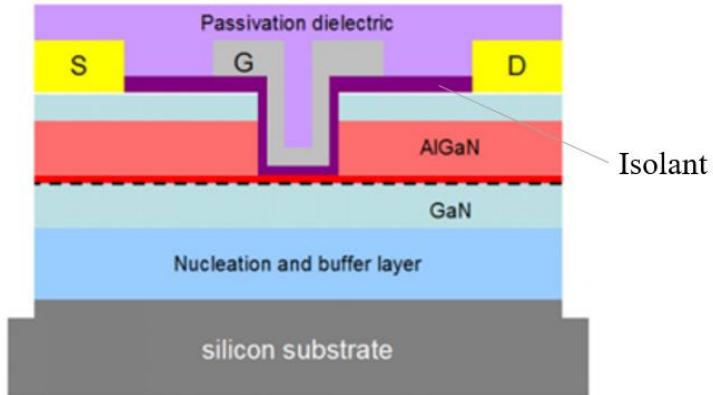

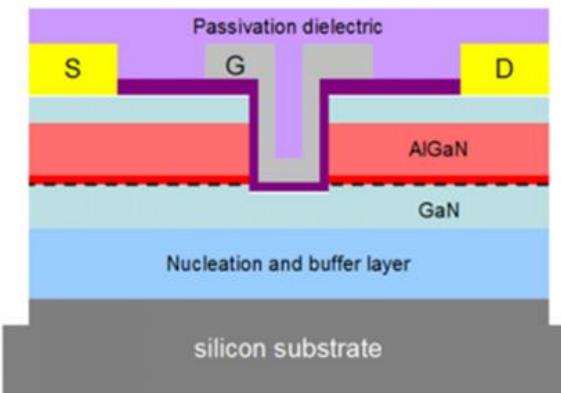

Les termes *MOS-HEMT* (*Metal Oxyde Semiconductor High Electron Mobility Transistor*) et *MIS-HEMT* (*Metal Insulator Semiconductor High Electron Mobility Transistor*) désignent tous les transistors GaN *HEMT* possédant un isolant sous la grille. Si l'isolant est un oxyde, on parle de *MOS-HEMT*. Si ce n'est pas le cas, on parle de *MIS-HEMT*. Différentes structures de *MOS(MIS)-HEMT* existent.

La première structure possible est le *recessed gate MOS(MIS)-HEMT*. Cette structure est identique au *recessed gate HEMT*, à la différence près qu'il y a un isolant sous la grille (Figure 8).

Figure 8 : structure recessed gate MOS(MIS)-HEMT, où la couche d'AlGaN est gravée partiellement (tiré de [4]).

Une deuxième structure possible est le *MOS(MIS)-HEMT* à gravure profonde, où la couche d'AlGaN est supprimée complètement sous la grille [4], comme présenté en Figure 9. Le gaz 2D est alors coupé. Le drain et la source doivent être connectés par une couche d'inversion pour rendre passant le composant [10] [32]. Le choix de l'isolant est critique : il impacte à la fois la mobilité du canal et la stabilité de la tension de seuil.

Figure 9 : structure MOS(MIS)-HEMT, où la couche d'AlGaN est gravée complètement (tiré de [4]).

La résistance spécifique des *MOS(MIS)-HEMT* à gravure profonde est supérieure à celle des *recessed gate HEMTs* puisque ces derniers bénéficient du gaz 2D d'électrons. Les premiers sont toutefois moins sensibles à la profondeur précise de gravure que les *HEMTs* et possèdent des tensions de seuil comprises entre 2 V et 5 V, ce qui peut éviter les remises en conduction intempestives [23].

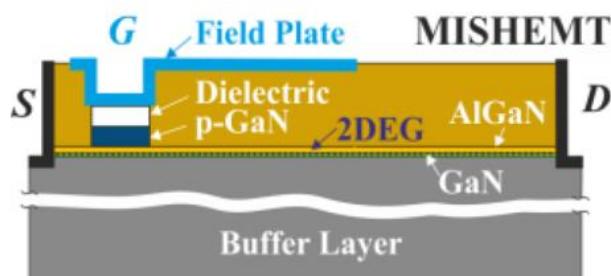

On trouve aussi une autre structure hybride, dont la grille comprend à la fois une couche de p-GaN et un isolant, décrite dans l'article [33] notamment (Figure 10). Le diélectrique est critique pour la fiabilité et mesure une dizaine de nanomètres d'épaisseur. La tension de seuil peut souffrir d'instabilité car des charges peuvent se piéger sur les bords du diélectrique [33]. La grille peut souffrir d'un effet tunnel qui contribue à augmenter la valeur du courant de grille.

Figure 10 : structure d'un MIS-HEMT (tiré de [33]).

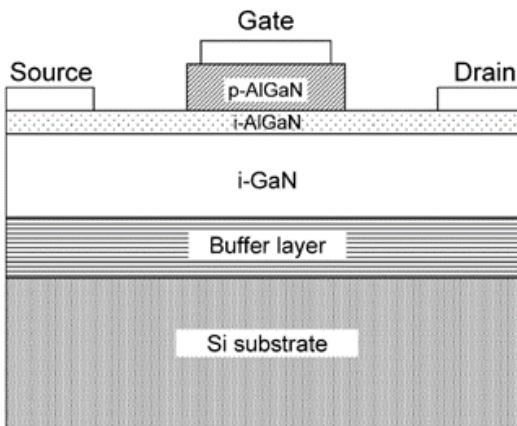

### 2.1.3 - HEMT avec grille p-GaN

Tout en restant dans la famille des *HEMT*, on peut appauvrir le gaz 2D en insérant une couche de p-GaN (ou p-AlGaN) sous la grille [8] [4]. Cette dernière possibilité reste la plus prometteuse, et est utilisée notamment chez les fondeurs GaN Systems et Panasonic [23]. Cela forme avec le métal de l'électrode de grille un contact métal/semiconducteur. Ce dernier peut se comporter comme un contact ohmique ou comme un contact schottky, en fonction du métal choisi et d'autres paramètres liés au procédé de fabrication. Si le contact est ohmique, il existe en permanence un courant de grille lorsque le transistor est à l'état passant (c'est le cas des transistors du fondeur Panasonic). Au contraire, si le contact est de type Schottky, ce courant est négligeable en dehors des phases de charge et de décharge de la grille (cette structure est celle du fondeur GaN Systems). Il faut noter que la fabrication d'un contact ohmique est délicate ; si celui-ci n'est pas parfaitement réalisé, la caractéristique électrique peut être de type contact Schottky. Il est possible qu'un fondeur annonce un contact d'un certain type (ohmique ou Schottky), mais qu'en réalité la grille se comporte différemment.

Figure 11 : Structure d'une grille de type P-AlGaN. Tiré de [34].

La grille p-GaN se comporte comme une diode, et est assez fragile. Un courant de grille trop important peut la détruire. La tension  $V_{GS}$  admissible est donc assez faible ( $-10\text{ V}/+7\text{ V}$  pour le fondeur GaN Systems par exemple).

Certains fondeurs combinent plusieurs techniques pour fabriquer leurs transistors. Il est possible de graver légèrement la couche d'AlGaN et d'utiliser en plus une grille p-GaN (cas de GaN Systems).

### 2.1.4 - HEMT avec injection de fluor (implanted gate)

Une autre possibilité est d'injecter du fluor en dessous de la grille (*implanted gate*) avec un traitement par plasma [8] [4] [23]. La charge négative des ions fluorés appauvrit le gaz 2D. Cela a pour inconvénient de dégrader la stabilité de la tension de seuil à haute température. On peut aussi introduire une couche à base d'oxydes de nickel en dessous de la grille, mais cette approche est peu répandue.

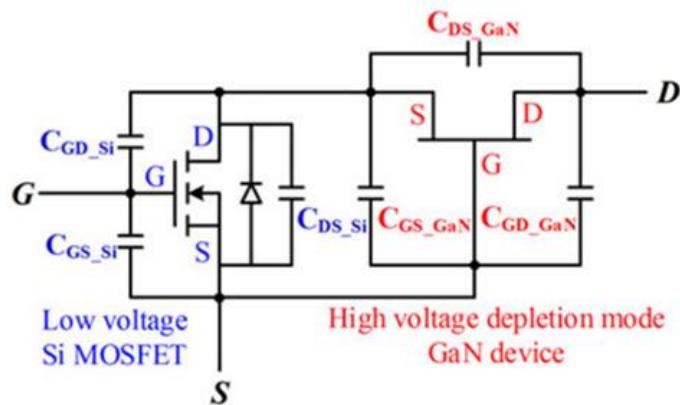

### 2.1.5 - Cascode

Pour obtenir un transistor normalement bloqué, une autre solution est d'associer en série un transistor GaN normalement passant avec un *MOSFET* silicium basse tension : c'est la structure cascode [13] (Figure 12). Elle est adaptée aux tensions supérieures à  $200\text{ V}$ , sinon la résistance passante ramenée par le *MOSFET* est trop importante [8]. Le transistor GaN peut être rendu passant ou bloqué en appliquant une tension de grille sur le *MOSFET* basse tension. La tension de seuil est de l'ordre de  $5\text{ V}$ , la commande est donc moins sensible aux bruits [14] [33] et il est possible d'utiliser un driver de *MOSFET* silicium classique fournissant une tension de commande égale à

15 V. Cette structure est intéressante car la structure d'un transistor GaN normalement passant est plus simple que celle d'un transistor normalement bloqué et qu'il est aisément d'ajouter en série un *MOSFET* silicium basse tension pour en faire un interrupteur normalement bloqué. Les pertes au blocage sont très faibles, ce qui en fait un bon choix pour des convertisseurs à fort courant [35]. La résistance passante spécifique est similaire à celle des structures p-GaN. Un autre avantage de cette structure est une meilleure robustesse car les grilles des transistors GaN à appauvrissement ne sont pas dopées et donc exemptes de défauts dans le cristal [36]. Les performances en commutation dépendent beaucoup des inductances parasites du package (connexion entre le *HEMT* et le *MOSFET* silicium) et de l'accord entre les capacités parasites des deux transistors [10].

Cette structure souffre cependant de certains inconvénients. Tout d'abord, la complexité du boîtier est accrue [3] puisqu'il y a deux puces à connecter entre elles. Dans le circuit de grille du transistor GaN, les inductances parasites des fils de bounding et les capacités parasites forment un circuit résonant très peu amorti [35]. Cela peut générer des oscillations qui sont parfois auto-entretenues [3], et d'autant plus fortes que la tension  $V_{DS}$  est grande. Ceci peut affecter les commutations. En conduction inverse, la diode du *MOSFET* conduit et il y a un temps de recouvrement non nul, ce qui augmente les pertes [13]. Le fait d'utiliser deux transistors pose aussi des soucis de coût [4].

Figure 12 : structure cascode avec les capacités parasites (tiré de [37]).

J'ai réalisé des essais de court-circuit sur des transistors cascode du fondeur Transphorm.

## 2.2 - Structures verticales

Les structures verticales ont des caractéristiques supérieures aux structures latérales, mais exigent en général une homo-épitaxie, c'est-à-dire un substrat en GaN, qui est coûteux, difficile à fabriquer et encore peu répandu [10]. Ces structures ont beaucoup moins de défauts dans la structure cristalline, et n'ont aucune différence de paramètre de maille. Ceci augmente leur fiabilité [3] et supprime le phénomène de résistance passante dynamique (partie 3 - ). Par ailleurs, cette structure est capable de résister au phénomène d'avalanche, contrairement à la structure latérale. En général, les niveaux de courant des transistors verticaux sont plus élevés que ceux de leurs homologues latéraux [3]. La taille de la puce sur le wafer est plus petite car il suffit d'augmenter l'épaisseur de la zone de drift pour augmenter la tenue en tension [38]. Les structures verticales seraient plutôt adaptées à de fortes puissances [3]. La gestion de la thermique est aussi facilitée par rapport aux structures latérales [3].

La société Avogy a déposé de nombreux brevets dans ce domaine et proposait des échantillons de diodes 600 V, 1200 V et 1700 V. Plus récemment, l'entreprise Nexgen montre sur son site des datasheets de transistors verticaux avec une tension de claquage de 700 V ou 1200 V [39]. Cependant, ces composants ne sont pas encore industrialisés. Par ailleurs, un transistor vertical à nanostructure 3D est présenté dans [40]. D'autres structures utilisant du GaN comme le CAVET

(*Current Aperture Vertical Electron Transistors*) [41] [38] ou le *MOSFET* à tranchées [42] permettent d'atteindre des tensions de claquage supérieures à 1200 V, mais utilisent de coûteux substrats en GaN, et font parfois appel à des étapes de croissance de cristal spécifiques.

Il existe cependant des structures verticales à substrat silicium, étudiées notamment par le MIT (*Massachusetts Institute of Technology*, USA) et par l'entreprise Cambridge Electronics Inc [10]. Cependant, en 2020, l'article [3] indiquait qu'aucun transistor GaN vertical n'était encore commercialisé même si ces composants font l'objet de beaucoup de recherches [3].

### 3 - Phénomène d'effondrement du courant (*current collapse*)

Les transistors GaN latéraux souffrent généralement de défauts dans la couche de GaN ou d'AlGaN, comme des dislocations ou des atomes étrangers (impuretés). On parle de pièges, qui s'activent ou se désactivent selon la tension appliquée. Ces pièges correspondent à des niveaux d'énergie dans le *gap* du GaN ou de l'AlGaN. Des charges peuvent se piéger et se dépiéger. La thèse de Fadi Zaki [43] indique que le phénomène de piégeage de charges est réversible mais peut affecter le comportement statique et dynamique des *HEMTs*.

Aussi appelé « résistance passante dynamique », le phénomène d'effondrement du courant dans les structures GaN latérales est directement lié aux pièges et reste un frein à la diffusion des transistors GaN [15]. Cela consiste en une augmentation temporaire de la résistance à l'état passant, qui est fonction de la tension drain-source  $V_{DS}$  supportée à l'état bloqué [10] et de la durée d'application de cette tension. Quand le transistor est bloqué, des charges peuvent se piéger dans les défauts du cristal ou aux interfaces entre couches dans la puce [44]. Cela génère des zones chargées négativement au sein du transistor, ce qui a deux effets : la répartition du champ électrique dans le transistor est modifiée, et le gaz 2D est perturbé. La résistance à l'état passant augmente alors, ainsi que les pertes [15], pouvant aller jusqu'à la destruction du composant [45].

On distingue deux types de piégeage [10]. Tout d'abord, des charges situées en surface peuvent se piéger à côté du bord de la grille ou du côté du drain quand le composant est à l'état bloqué. Ces charges se comportent comme une grille virtuelle et affaiblissent le gaz 2D. Le second mécanisme est le piégeage d'électrons à haute énergie en profondeur, dans la couche tampon située au-dessus du substrat notamment. Cela affaiblit aussi le gaz 2D, augmente la résistance à l'état passant et peut endommager le transistor sur le long-terme. Le phénomène est dynamique car la résistance à l'état passant se met à augmenter au fil des commutations.

Les fondeurs ont fait beaucoup de progrès pour contrer le phénomène de courant de collapse, en utilisant par exemple des plaques de champ pour redistribuer le champ électrique entre le drain et la grille, ou en connectant le substrat à la source. Panasonic aurait éliminé le courant de collapse grâce à l'ajout d'une structure dopée P à côté du drain [10] [44] (structure *HD-GIT*). L'article [14] étudie les mécanismes de piégeage de charges causés par l'application d'une tension négative pulsée sur la grille de transistors cascode. Ils constatent une dégradation de la résistance passante et du courant de drain maximal ainsi qu'un déplacement de la tension de seuil. Les auteurs de l'article [15] caractérisent le phénomène de résistance passante dynamique sur des transistors GS66508T du fondeur GaN Systems. Ils conseillent de faire cette caractérisation à haute fréquence et haute température pour être dans des conditions proches d'un usage réel dans un convertisseur. La résistance passante dynamique augmente en effet fortement avec la température.

## 4 - Utilisation du GaN dans des convertisseurs

En 2017, il n'y avait que trois fondeurs qui proposaient des transistors GaN à enrichissement à la vente, dont une structure cascode [10]. L'article [3], paru en 2020, indiquait les applications industrielles possibles du GaN dans les secteurs des voitures électriques et hybrides, de l'avion plus électrique, du navire plus électrique, des trains électriques et des véhicules tout terrain électrifiés. En 2021, on compte plus de neuf fondeurs mais les transistors GaN ne sont pas encore présents dans ces secteurs.

En 2013, l'article [13] montrait déjà l'utilisation de transistors GaN cascode dans un convertisseur résonnant LLC de 300 W avec une fréquence de commutation de 1 MHz.

En 2014, le fondeur *EPC* publie un article [46] montrant l'utilisation de leurs transistors GaN basse tension dans un convertisseur DC/DC *POL* (*Point Of Load*) (entrée : 12 – 28 V ; sortie : 1,2 V) travaillant à 1 MHz. La comparaison faite avec des transistors silicium donne un net avantage au GaN avec presque 4 points de rendement de plus pour ce dernier. Un peu plus tard, en 2015, les auteurs de l'article [47] intègrent des transistors cascode de *Transphorm* dans un convertisseur *PFC* (*Power Factor Corrector*). Ce dernier atteint un rendement maximal de 99 % et une densité de puissance égale à 220 W/in<sup>3</sup>. Ensuite, courant 2016, l'article [48] présente l'utilisation de transistors du fondeur *GaN Systems* dans un onduleur triphasé de 10 kW. Le rendement atteint 98,8 % et le volume n'est que de 0,7 L. Puis, en 2017, l'article [49] présente un convertisseur résonant LLC à commutation douce à base de transistors GaN cascode du fondeur *Transphorm*. Leur tension de claquage vaut 600 V et la tension d'entrée du convertisseur est de 400 V. Les auteurs comparent les pertes entre ces derniers et des transistors silicium et il apparaît que le GaN présente des pertes 50 % plus faibles.

Plus tard, en 2019, dans l'article [50], les auteurs conçoivent et testent un convertisseur *NPC* (*Neutral Point Clamped*) à trois niveaux à base de transistors du fondeur *GaN Systems* (leur tension de claquage est de 650 V) et de diodes SiC. Leur prototype atteint un rendement de 98%. Ces transistors ont un boîtier monté en surface, ce qui a impacté la façon de router le convertisseur ainsi que son refroidissement. Toujours en 2019, les auteurs de l'article [12] passent en revue plus de 160 papiers montrant une intégration de transistors GaN dans des convertisseurs de puissance de plus de 500 W de différentes familles (DC/DC, DC/AC et AC/DC). Il ressort de tout cela que ces composants permettent de concevoir des convertisseurs à haut rendement (jusqu'à 99,8 %) dans la gamme moyenne tension, de moyenne à forte puissance (jusqu'à 80 kW). La fréquence de travail des systèmes passés en revue s'échelonne de 100 kHz à plus de 1 MHz. Onze papiers font état d'une fréquence supérieure à 1 MHz. La grande majorité des convertisseurs étudiés a un rendement compris entre 95% et 99% ; plus des deux tiers des convertisseurs ont une densité de puissance supérieure à 100 – 200 W/in<sup>3</sup> et le maximum atteint est de 9,5 kW/in<sup>3</sup>.

Enfin, en 2020, l'article [51] montre l'utilisation de transistors GaN du fondeur *EPC* dans un convertisseur DC/DC résonant à commutations douces à 1 MHz qui pourrait être utilisé dans le domaine spatial. Une comparaison est faite avec des *MOSFETs* silicium commutant à 100 kHz. Il est montré que la densité de puissance est accrue d'environ 80 % avec le GaN, et que le rendement reste identique.

Si les transistors GaN sont pour le moment absents dans l'industrie des transports, on trouve une application industrielle dans le domaine des chargeurs USB. Depuis 2018, il existe dans le commerce des chargeurs intégrant des transistors GaN [5] pour alimenter un téléphone portable, une tablette ou un ordinateur. C'est la seule utilisation industrielle du GaN recensée en 2021.

## 5 - Conclusion et futures tendances

Les défis à relever pour permettre la diffusion massive du GaN dans l'industrie sont : la robustesse et la fiabilité en court-circuit qui sont encore limitées, la tension de claquage encore limitée, la complexité de la commande de la grille, la gestion de la thermique et la conception des boîtiers des transistors pour utiliser la pleine capacité de ces composants, et assurer une fiabilité à long terme [3]. Enfin, le coût élevé des composants freine encore leur adoption.

Concernant la robustesse des transistors GaN, elle est encore insuffisante en court-circuit lorsqu'on les utilise sous des tensions proches de la tension de claquage. La fiabilité est, elle aussi, encore perfectible même si certains composants comme le *HD-GIT* de Panasonic peuvent supporter de nombreux courts-circuits sous une tension de bus élevée.

La tension de claquage encore limitée des transistors GaN du commerce (650 V) restreint aujourd'hui leur usage [50]. Il est encore difficile de fabriquer des transistors GaN haute tension (1200 V) car cela nécessite des améliorations et des innovations dans le procédé de fabrication, au niveau du substrat. L'utilisation du nitrate d'aluminium polycristallin (AlN) comme substrat est prometteur pour fabriquer des composants 1200 V, car son coefficient d'expansion thermique est plus proche de celui du GaN par rapport aux substrats silicium classique [3]. Le substrat AlN autorise le dépôt d'une couche plus épaisse de GaN (avec des wafers de 200 mm), ce qui est nécessaire pour augmenter la tenue en tension.

Le routage du PCB d'un convertisseur à base de GaN est critique [46] à cause des vitesses de commutation élevées. Les inductances parasites peuvent avoir un impact important sur les pertes [13]. Les circuits de commande doivent être adaptés aux forts  $di/dt$  et  $dv/dt$ , ce qui impose un routage très soigné. Des oscillations peuvent apparaître au niveau de la grille à cause des éléments parasites du circuit, la commande de la grille est donc critique [14]. Par ailleurs, du fait de leur vitesse de commutation, les transistors GaN posent des problèmes de pollution électromagnétique [3]. La grille des composants GaN discrets est vulnérable au bruit et aux surtensions causées par les commutations très rapides. La tension de seuil est très basse, ce qui peut causer des remises en conduction intempestives lors du blocage. A titre d'exemple, le choix de la valeur de la résistance de grille pour l'amorçage est critique : trop faible, elle entraîne des oscillations et donc des pertes de commandes importantes ; trop grande, elle ralentit les commutations et augmente aussi les pertes. L'intégration monolithique du driver, des protections et du transistor GaN (voire d'un demi-pont complet) a de nombreux avantages [3] : un meilleur contrôle des inductances parasites, un meilleur contrôle du  $dv/dt$ , la possibilité d'intégrer des protections (au démarrage, contre les surcourants, contre un échauffement excessif et contre les courts-circuits). Cette intégration permet une conception plus modulaire du convertisseur, augmente sa densité de puissance et permet aussi de réduire les coûts.

Le boîtier d'un transistor a de nombreuses fonctions : il protège la puce, permet de la monter sur un PCB et participe à l'évacuation de la chaleur. La conception d'un boîtier et de ses connexions avec la puce est délicate car elle doit prendre en compte un besoin d'isolation contre de fortes tensions et une tenue à de forts courants, sans dégrader les performances de la puce. Le boîtier joue un rôle important dans la fiabilité du transistor. Les transistors GaN nécessitent un boîtier spécifique dédié, avec des connexions optimisées vers le radiateur. Le refroidissement est en effet critique du fait de la taille réduite de la puce.

La minimisation du poids et du volume des systèmes embarqués est un des objectifs principaux de l'industrie des transports. La grande densité de puissance et la fréquence de commutation élevée du GaN en font un très bon candidat pour les convertisseurs de puissance du secteur des transports.

En effet, cela permet de diminuer la taille des composants passifs et donc d'alléger le véhicule. Si les différentes contraintes listées dans cette partie restent des freins à la diffusion des transistors GaN, il est probable que ces derniers soient massivement adoptés dans les années à venir [52].

## Références :

- [1] Ministère de la transition écologique et Institute for climate economics, « Chiffres clés du climat - France, Europe et Monde ». déc. 2020. [En ligne]. Disponible sur : <https://www.statistiques.developpement-durable.gouv.fr/edition-numerique/chiffres-cles-du-climat>

- [2] Institut Français du Pétrole, « Les énergies pour le transport : avantages et inconvénients ». déc. 2008. [En ligne]. Disponible sur : [https://inis.iaea.org/collection/NCLCollectionStore/\\_Public/42/016/42016175.pdf](https://inis.iaea.org/collection/NCLCollectionStore/_Public/42/016/42016175.pdf)

- [3] N. Keshmiri, D. Wang, B. Agrawal, R. Hou, et A. Emadi, « Current Status and Future Trends of GaN HEMTs in Electrified Transportation », IEEE Access, vol. 8, p. 70553-70571, 2020, doi: 10.1109/ACCESS.2020.2986972.

- [4] M. Su, C. Chen, et S. Rajan, « Prospects for the application of GaN power devices in hybrid electric vehicle drive systems », Semicond. Sci. Technol., vol. 28, no 7, p. 074012, juin 2013, doi: 10.1088/0268-1242/28/7/074012.

- [5] Ganfast, « Site internet de ganfast ». [En ligne]. Disponible sur : <https://ganfast.com/products/>

- [6] H. Schefer, L. Fauth, T. H. Kopp, R. Mallwitz, J. Fribe, et M. Kurrat, « Discussion on Electric Power Supply Systems for All Electric Aircraft », IEEE Access, vol. 8, p. 84188-84216, 2020, doi: 10.1109/ACCESS.2020.2991804.

- [8] A. Lidow, M. De Rooij, J. Strydom, D. Reusch, et J. Glaser, GaN Transistors for Efficient Power Conversion.

- [9] S. Nakamura et M. R. Krames, « History of Gallium-Nitride-Based Light-Emitting Diodes for Illumination », Proc. IEEE, vol. 101, no 10, p. 2211-2220, oct. 2013, doi: 10.1109/JPROC.2013.2274929.

- [10] E. A. Jones, F. F. Wang, et D. Costinett, « Review of Commercial GaN Power Devices and GaN-Based Converter Design Challenges », IEEE J. Emerg. Sel. Top. Power Electron., vol. 4, no 3, p. 707-719, sept. 2016, doi: 10.1109/JESTPE.2016.2582685.

- [11] A. Castellazzi, « Opportunities and challenges of integrated WBG power electronics development », in 2021 Third International Symposium on 3D Power Electronics Integration and Manufacturing (3D-PEIM), juin 2021, p. 1-6. doi: 10.1109/3D-PEIM49630.2021.9497265.

- [12] C.-T. Ma et Z.-H. Gu, « Review of GaN HEMT Applications in Power Converters over 500 W », Electronics, vol. 8, no 12, Art. no 12, déc. 2019, doi: 10.3390/electronics8121401.

- [13] X. Huang, Z. Liu, Q. Li, et F. C. Lee, « Evaluation and Application of 600 V GaN HEMT in Cascode Structure », IEEE Trans. Power Electron., vol. 29, no 5, p. 2453-2461, mai 2014, doi: 10.1109/TPEL.2013.2276127.

- [14] S. Elangovan, S. Cheng, et E. Y. Chang, « Reliability Characterization of Gallium Nitride MIS-HEMT Based Cascode Devices for Power Electronic Applications », Energies, vol. 13, no 10, Art. no 10, janv. 2020, doi: 10.3390/en13102628.

- [15] Y. Li et al., « Evaluation and Analysis of Temperature-Dependent Dynamic  $\$R_{DS(on)}\$$  of GaN Power Devices Considering High-Frequency Operation », IEEE J. Emerg. Sel. Top. Power Electron., vol. 8, no 1, p. 111-123, mars 2020, doi: 10.1109/JESTPE.2019.2947575.

- [16] J. Wu, W. Meng, F. Zhang, G. Dong, et J. Shu, « A Short-Circuit Protection Circuit With Strong Noise Immunity for GaN HEMTs », *IEEE Trans. Power Electron.*, vol. 36, no 2, p. 2432-2442, févr. 2021, doi: 10.1109/TPEL.2020.3013984.

- [17] J. Acuna, J. Walter, et I. Kallfass, « Very Fast Short Circuit Protection for Gallium-Nitride Power Transistors Based on Printed Circuit Board Integrated Current Sensor », in 2018 20th European Conference on Power Electronics and Applications (EPE'18 ECCE Europe), sept. 2018, p. P.1-P.10.

- [18] X. Huang et al., « Experimental study of 650V AlGaN/GaN HEMT short-circuit safe operating area (SCSOA) », in 2014 IEEE 26th International Symposium on Power Semiconductor Devices IC's (ISPSD), juin 2014, p. 273-276. doi: 10.1109/ISPSD.2014.6856029.

- [19] R. Mitova, R. Ghosh, U. Mhaskar, D. Klikic, M.-X. Wang, et A. Dentella, « Investigations of 600-V GaN HEMT and GaN Diode for Power Converter Applications », *IEEE Trans. Power Electron.*, vol. 29, no 5, p. 2441-2452, mai 2014, doi: 10.1109/TPEL.2013.2286639.

- [20] J. Sun, J. Wei, Z. Zheng, et K. J. Chen, « Short Circuit Capability Characterization and Analysis of p-GaN Gate High-Electron-Mobility Transistors Under Single and Repetitive Tests », *IEEE Trans. Ind. Electron.*, vol. 68, no 9, p. 8798-8807, sept. 2021, doi: 10.1109/TIE.2020.3009603.

- [21] D. Ueda et al., « Present and future prospects of gan-based power electronics », in 2008 9th International Conference on Solid-State and Integrated-Circuit Technology, oct. 2008, p. 1078-1081. doi: 10.1109/ICSICT.2008.4734738.

- [22] GaN Systems, « GN001 Application Note "An introduction to GaN Enhancement-mode HEMTs » . avr. 16, 2020.

- [23] G. Greco, F. Iucolano, et F. Roccaforte, « Review of technology for normally-off HEMTs with p-GaN gate », *Mater. Sci. Semicond. Process.*, vol. 78, p. 96-106, mai 2018, doi: 10.1016/j.mssp.2017.09.027.

- [24] C. Abbate, F. Iannuzzo, et G. Busatto, « Thermal instability during short circuit of normally-off AlGaN/GaN HFETs », *Microelectron. Reliab.*, vol. 53, no 9, p. 1481-1485, sept. 2013, doi: 10.1016/j.microrel.2013.07.119.

- [25] H. Hamza K., D. Nirmal, et L. Arivazhagan, « Impact of AlGaN Back Barrier in AlGaN/GaN HEMT on GaN substrate », in 2020 5th International Conference on Devices, Circuits and Systems (ICDCS), mars 2020, p. 290-293. doi: 10.1109/ICDCS48716.2020.9243601.

- [26] H. Ohta, T. Nakamura, et T. Mishima, « High quality free-standing GaN substrates and their application to high breakdown voltage GaN p-n diodes », in 2016 IEEE International Meeting for Future of Electron Devices, Kansai (IMFEDK), juin 2016, p. 1-2. doi: 10.1109/IMFEDK.2016.7521696.

- [27] T. Yoshida et al., « Fabrication of 3-in GaN substrates by hydride vapor phase epitaxy using void-assisted separation method », *J. Cryst. Growth*, vol. 310, no 1, p. 5-7, janv. 2008, doi: 10.1016/j.jcrysgro.2007.10.014.

- [28] M. Imanishi, S. Usami, M. Maruyama, M. Yoshimura, et Y. Mori, « Growth of a High Quality GaN Wafer from Point Seeds by the Na-Flux Method », in 2021 28th International Workshop on Active-Matrix Flatpanel Displays and Devices (AM-FPD), juin 2021, p. 70-72. doi: 10.23919/AM-FPD52126.2021.9499151.

- [29] T. Nagahisa, H. Ichijoh, T. Suzuki, A. Yudin, A. O. Adan, et M. Kubo, « Robust 600 V GaN high electron mobility transistor technology on GaN-on-Si with 400 V, 5  $\mu$ s load-short-circuit withstand capability », *Jpn. J. Appl. Phys.*, vol. 55, no 4S, p. 04EG01, févr. 2016, doi: 10.7567/JJAP.55.04EG01.

- [30] H. W. Then et al., « Gallium Nitride and Silicon Transistors on 300 mm Silicon Wafers Enabled by 3-D Monolithic Heterogeneous Integration », *IEEE Trans. Electron Devices*, vol. 67, no 12, p. 5306-5314, déc. 2020, doi: 10.1109/TED.2020.3034076.

- [31] W. B. Lanford, T. Tanaka, Y. Otoki, et I. Adesida, « Recessed-gate enhancement-mode GaN HEMT with high threshold voltage », *Electron. Lett.*, vol. 41, no 7, p. 449-450, mars 2005, doi: 10.1049/el:20050161.

- [32] H. Kambayashi et al., « Over 100A operation normally-off AlGaN/GaN hybrid MOS-HFET on Si substrate with high-breakdown voltage », *Solid-State Electron.*, vol. 54, no 6, p. 660-664, juin 2010, doi: 10.1016/j.sse.2010.01.001.

- [33] M. Fernández et al., « Short-Circuit Study in Medium-Voltage GaN Cascodes, p-GaN HEMTs, and GaN MISHEMTs », *IEEE Trans. Ind. Electron.*, vol. 64, no 11, p. 9012-9022, nov. 2017, doi: 10.1109/TIE.2017.2719599.

- [34] Y. Uemoto et al., « Gate Injection Transistor (GIT)—A Normally-Off AlGaN/GaN Power Transistor Using Conductivity Modulation », *IEEE Trans. Electron Devices*, vol. 54, no 12, p. 3393-3399, déc. 2007, doi: 10.1109/TED.2007.908601.

- [35] P. Xue, L. Maresca, M. Riccio, G. Breglio, et A. Irace, « Experimental Study on the Short-Circuit Instability of Cascode GaN HEMTs », *IEEE Trans. Electron Devices*, vol. 67, no 4, p. 1686-1692, avr. 2020, doi: 10.1109/TED.2020.2974518.

- [36] S. Ben-Yaakov et L. Van de Perre, « A Novel Circuit Topology for Turning a ‘Normally On’ GaN Transistor into ‘Normally Off’ that Can be Driven by Popular Drivers ». juin 2018.

- [37] X. Huang, W. Du, F. C. Lee, Q. Li, et W. Zhang, « Avoiding Divergent Oscillation of a Cascode GaN Device Under High-Current Turn-Off Condition », *IEEE Trans. Power Electron.*, vol. 32, no 1, p. 593-601, janv. 2017, doi: 10.1109/TPEL.2016.2532799.

- [38] S. Chowdhury, B. L. Swenson, M. H. Wong, et U. K. Mishra, « Current status and scope of gallium nitride-based vertical transistors for high-power electronics application », *Semicond. Sci. Technol.*, vol. 28, no 7, p. 074014, juin 2013, doi: 10.1088/0268-1242/28/7/074014.

- [39] Nexgen, « Site internet de Nexgen ». [En ligne]. Disponible sur: <https://nexgenpowersystems.com/datasheets>

- [40] K. Stremmel et al., « Vertical 3D gallium nitride field-effect transistors based on fin structures with inverted p-doped channel », *Semicond. Sci. Technol.*, vol. 36, p. 9, nov. 2020, doi: 10.1088/1361-6641/abc5ff.

- [41] I. Ben-Yaacov, Y.-K. Seck, U. K. Mishra, et S. P. DenBaars, « AlGaN/GaN current aperture vertical electron transistors with regrown channels », *J. Appl. Phys.*, vol. 95, no 4, p. 2073-2078, févr. 2004, doi: 10.1063/1.1641520.

- [42] T. Oka, T. Ina, Y. Ueno, et J. Nishii, « 1.8 mΩ·cm<sup>2</sup> vertical GaN-based trench metal-oxide-semiconductor field-effect transistors on a free-standing GaN substrate for 1.2-kV-class operation », *Appl. Phys. Express*, vol. 8, no 5, p. 054101, avr. 2015, doi: 10.7567/APEX.8.054101.

- [43] F. N. F. Zaki, « Characterization, modeling and aging behavior of GaN power transistors », phdthesis, Université Paris Saclay (COmUE), 2018. Consulté le : sept. 09, 2021. [En ligne]. Disponible sur : <https://tel.archives-ouvertes.fr/tel-01794546>

- [44] « Panasonic GaN power transistors white paper ».

- [45] G. Meneghesso et al., « Reliability and parasitic issues in GaN-based power HEMTs: a review », *Semicond. Sci. Technol.*, vol. 31, no 9, p. 093004, août 2016, doi: 10.1088/0268-1242/31/9/093004.

- [46] D. Reusch et J. Strydom, « Understanding the Effect of PCB Layout on Circuit Performance in a High-Frequency Gallium-Nitride-Based Point of Load Converter », *IEEE Trans. Power Electron.*, vol. 29, no 4, p. 2008-2015, avr. 2014, doi: 10.1109/TPEL.2013.2266103.

- [47] Z. Liu, F. C. Lee, Q. Li, et Y. Yang, « Design of GaN-based MHz totem-pole PFC rectifier », in 2015 IEEE Energy Conversion Congress and Exposition (ECCE), sept. 2015, p. 682-688. doi: 10.1109/ECCE.2015.7309755.

- [48] H. Li, X. Li, Z. Zhang, C. Yao, et J. Wang, « Design consideration of high power GaN inverter », in 2016 IEEE 4th Workshop on Wide Bandgap Power Devices and Applications (WiPDA), nov. 2016, p. 23-29. doi: 10.1109/WiPDA.2016.7799904.

- [49] W. Zhang, F. Wang, D. J. Costinett, L. M. Tolbert, et B. J. Blalock, « Investigation of Gallium Nitride Devices in High-Frequency LLC Resonant Converters », IEEE Trans. Power Electron., vol. 32, no 1, p. 571-583, janv. 2017, doi: 10.1109/TPEL.2016.2528291.

- [50] P. Grzejszczak, A. Kulpa, et R. Barlik, « Design of a high-efficiency three-phase three-level NPC converter based on GaN HEMT and SiC SB diode », in 2019 Progress in Applied Electrical Engineering (PAEE), juin 2019, p. 1-6. doi: 10.1109/PAEE.2019.8788993.

- [51] E. Maset et al., « Optimized Design of 1 MHz Intermediate Bus Converter Using GaN HEMT for Aerospace Applications », Energies, vol. 13, p. 6583, déc. 2020, doi: 10.3390/en13246583.

- [52] D. Bisi et al., « Short-Circuit Capability Demonstrated for GaN Power Switches », in 2021 IEEE Applied Power Electronics Conference and Exposition (APEC), juin 2021, p. 370-375. doi: 10.1109/APEC42165.2021.9486987.